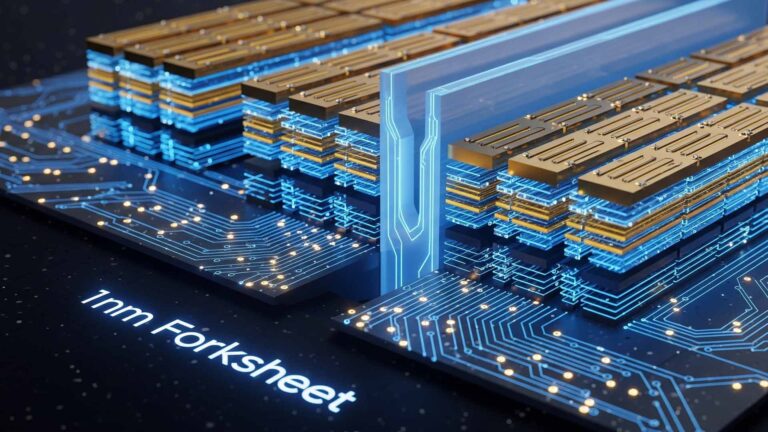

Samsung’un yarı iletken yol haritasına ilişkin ortaya çıkan yeni bilgiler, şirketin uzun vadeli planlarında oldukça iddialı bir hedefe odaklandığını gösteriyor. Güney Koreli teknoloji devi, 1 nanometre (nm) üretim sürecini 2031 yılında hayata geçirmeyi planlıyor.

Samsung’un yarı iletken yol haritasına ilişkin ortaya çıkan yeni bilgiler, şirketin uzun vadeli planlarında oldukça iddialı bir hedefe odaklandığını gösteriyor. Güney Koreli teknoloji devi, 1 nanometre (nm) üretim sürecini 2031 yılında hayata geçirmeyi planlıyor. Şirketin halihazırda ikinci ve üçüncü nesil 2 nm GAA (Gate-All-Around) süreçleri üzerinde çalıştığı bilinirken bu çalışmaların paralelinde çok daha ileri bir üretim teknolojisinin temellerinin atıldığı ifade ediliyor. Raporlara göre Samsung’un bu alandaki araştırma ve geliştirme faaliyetlerini 2030 yılına kadar tamamlaması, ardından da üretim aşamasına geçmesi hedefleniyor.

Transistörlerde “Fork sheet” dönemi

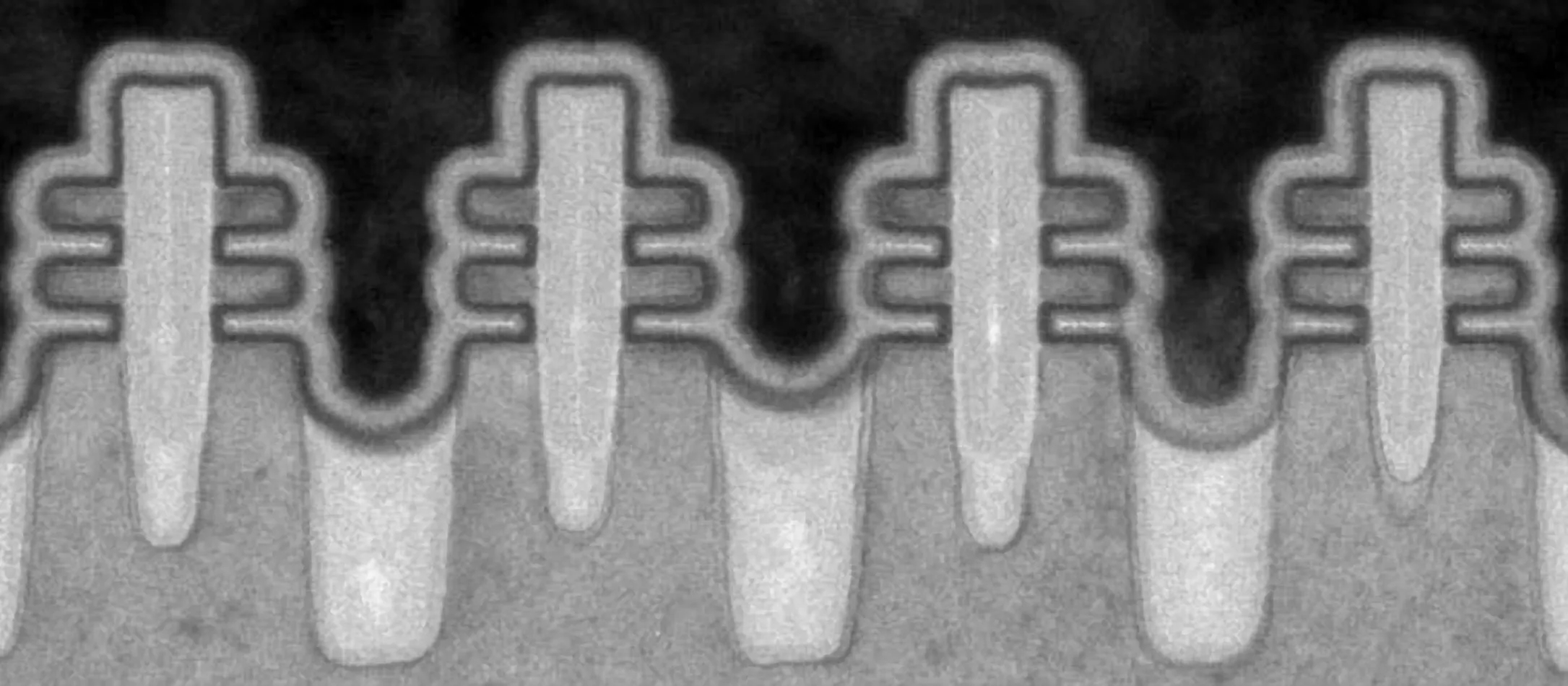

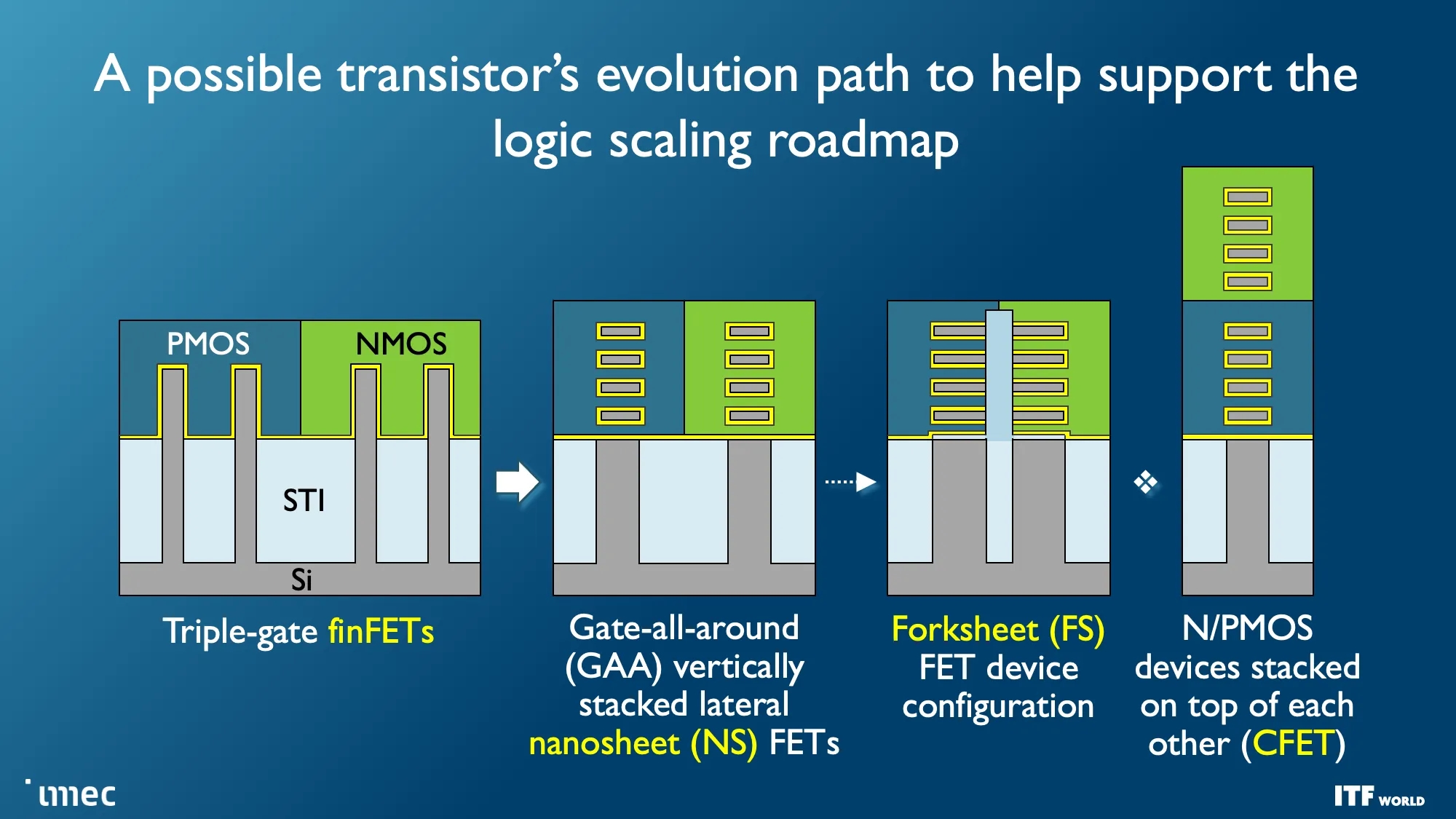

1 nm seviyesine geçiş yalnızca boyut küçültme anlamına gelmiyor aynı zamanda mimari açıdan da köklü değişiklikler gerektiriyor. Samsung’un bu noktada “fork sheet” adı verilen yeni bir yaklaşımı benimsemeye hazırlandığı belirtiliyor.

Bilmeyenler için fork sheet, nanosheet tabanlı transistörlerin sınırlarını aşmak için geliştirilen ara bir mimari olarak tanımlanıyor. Bu yapıda transistörler, aralarına yerleştirilen yalıtkan bir duvarın iki tarafına çiftler halinde konumlandırılıyor. Bu duvar sayesinde NMOS ve PMOS gibi farklı transistör tipleri birbirine daha yakın yerleştirilebiliyor ve performansı düşüren kapasitans artışı engelleniyor. Böylece aynı alanda daha yüksek yoğunluk elde edilirken daha geniş nanosheet kullanımıyla performans artışı da mümkün hale geliyor. Ayrıca fork sheet yaklaşımı, gelecekte hedeflenen ancak üretimi çok daha karmaşık olan CFET mimarisine geçişte bir ara adım olarak görülüyor.

Mevcut 2 nm üretim süreçlerinde kullanılan GAA teknolojisi, akım yolunu üç kanaldan dört kanala çıkararak enerji verimliliğini artırıyor. Ancak aynı yöntemin daha küçük ölçekte yeterli olmayacağı değerlendiriliyor. Bu nedenle Samsung, fork sheet mimarisiyle transistör yoğunluğunu artırmayı hedefliyor.

Mevcut 2 nm üretim süreçlerinde kullanılan GAA teknolojisi, akım yolunu üç kanaldan dört kanala çıkararak enerji verimliliğini artırıyor. Ancak aynı yöntemin daha küçük ölçekte yeterli olmayacağı değerlendiriliyor. Bu nedenle Samsung, fork sheet mimarisiyle transistör yoğunluğunu artırmayı hedefliyor. Bu yaklaşımda, GAA yapılarının arasına iletken olmayan bir “duvar” yerleştirilerek transistörler arasındaki boşluk daha verimli kullanılıyor. Bu sayede, aynı çip alanı içerisinde çok daha fazla transistör konumlandırılabiliyor.

Öte yandan Samsung’un daha önce gündeme gelen 1.4 nm sürecine ilişkin planlarında ise dikkat çekici değişiklikler yaşanmıştı. İlk etapta bu teknolojinin iptal edildiği yönünde iddialar ortaya atılsa da sonrasında sürecin 2028 yılına ertelendiği öne sürüldü. Bu kararın arkasında, şirketin kaynaklarını daha çok 2 nm GAA teknolojisine yönlendirme isteğinin yattığı düşünülüyor.